MIC-GPU: High-Performance Computing for Medical Imaging on Programmable Graphics Hardware (GPUs)

## **GPU Hardware**

Klaus Mueller, Ziyi Zheng, Eric Papenhausen

Stony Brook University

Computer Science

Stony Brook, NY

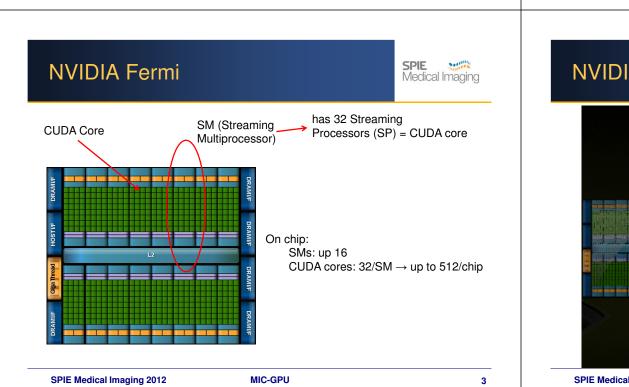

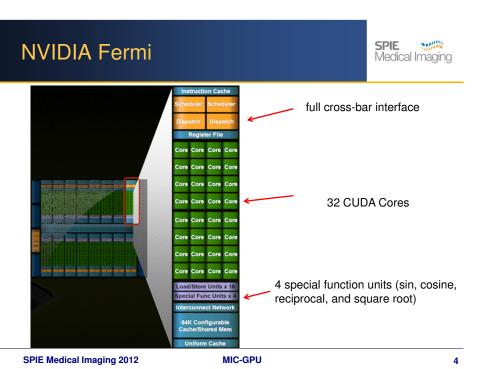

## **NVIDIA Fermi Architecture**

#### GeForce 500 series $\rightarrow$ consumer graphics board

• 1.5 GB DRAM

#### Tesla 2000 series $\rightarrow$ general computing board

• 6 GB DRAM

**SPIE Medical Imaging 2012**

- 2 x double precision performance

- ECC (Error Correcting Code) memory

#### Quadro 6000 series $\rightarrow$ professional graphics board

• Similar as Tesla but with video output

MIC-GPU

2

## Host and Device

## $\text{Host} \to \text{CPU}$

- controls program flow

- manages threads

- loads GPU programs (kernels)

- has host memory

$\text{Device} \to \text{GPU}$

- loads data

- performs computations

- has device memory

## Heterogeneous programming model

# SPIE Medical Imaging 2012 MIC-GPU 5 SPIE Medical Imaging 2012 MIC-GPU

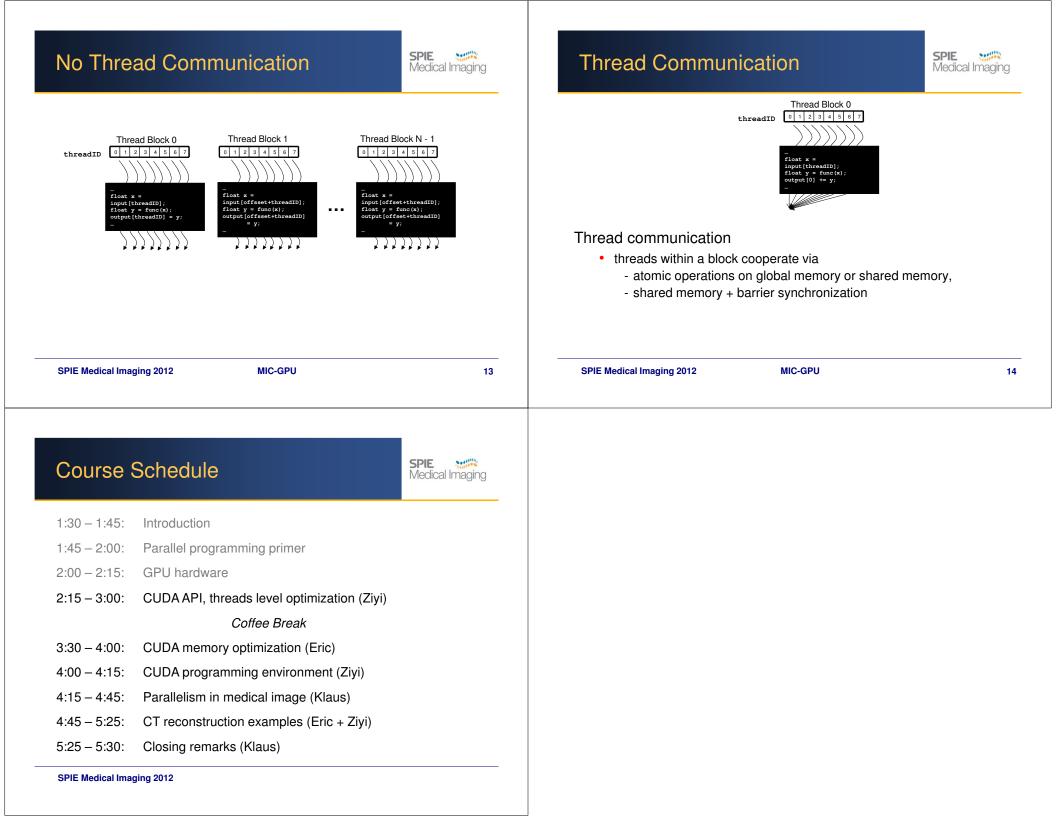

## Thread Hierarchy: Fine Grain

execute the same instruction simultaneously with different data

A warp is 32 threads (fixed)

## One SM can maintain 48 warps simultaneously

- keep one warp active while 47 wait for memory → latency hiding

- 32 threads × 48 warps ×16 SMs → 24,576 threads !

SPIE

Medical Imagino

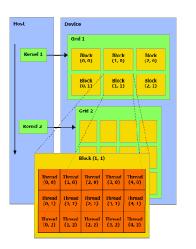

## Thread Hierarchy : Coarse Grain

#### Parallelism is exposed as threads

- all threads run the same code

- a thread runs on one core

#### The threads divide into blocks

- each block has a unique ID  $\rightarrow$  block ID

- each thread has a unique ID within a block → thread ID

- block ID and thread ID can be used to compute a *global ID*

### The blocks form a grid

Block/grid size can be set in program

SPIE

Host

Kerne

Kernel

Device

Grid 1

(0, 0)

Block (0, 1)

Grid 2

Thread Thread Thread

Thread Thread Thread

0.0.0) (1.0.0) (2.0.0) (3.0.0

Block (1, 1)

Medical Imaging

Block (2, 0)

Block (2, 1)

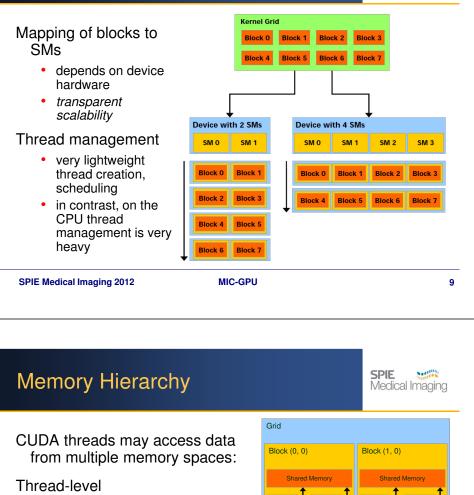

## **CUDA Hardware Implementation**

SPIE Medical Imaging

Upon invoking a CUDA program from the host:

## **Block-level**

- blocks are serially distributed to SMs

- threads of a block execute on one SM

- as thread blocks terminate, new blocks are launched on vacated SMs

## Thread-level

- each SM launches warps of threads

- · SM schedules and executes warps that are ready to run

- · as warps and thread blocks complete, resources are freed

7

## Mapping the Architecture to Parallel Programs

#### registers (fast)

local memory to handle register spills (slow)

#### **Block-level**

shared memory

#### Grid-level

- global memory

- constant memory (read-only)

- texture memory (read-only)

| Block (0, 0)       |                 | Block (1, 0)    |                 |

|--------------------|-----------------|-----------------|-----------------|

| Shared Memory      |                 | Shared Memory   |                 |

| Registers          | Registers       | Registers       | Registers       |

| Thread (0, 0)      | Thread (1, 0)   | Thread (0, 0)   | Thread (1, 0    |

| Local<br>Memory    | Local<br>Memory | Local<br>Memory | Local<br>Memory |

| Global<br>Memory   |                 |                 | Ť               |

| Constant<br>Memory |                 |                 |                 |

| Texture<br>Memory  |                 |                 |                 |

SPIE

Setting

Medical Imaging

## Block Scheduling: Example

## Threads are assigned to SMs in block granularity

• up to 8 blocks to each SM as resource allows

### An SM can take up to 1,536 threads

- could be 512 (threads/block) \* 3 blocks

- or 256 (threads/block) \* 6 blocks, etc.

## The optimal block size depends on:

- how much latency needs to be hidden (larger blocks)

- how much memory is needed per thread (smaller blocks)

SPIE Medical Imaging 2012

MIC-GPU

10

## Memory Hierarchy

Memory **On-chip** Cached Access Local Ν Υ RW Υ Υ Shared RW Global Ν 1D RW Constant Ν Υ R R Texture Ν 1-3D

## Code development strategy

- start by using just global memory

- then optimize

- more about this later

SPIE Medical Imaging

SPIE

Setting

Medical Imaging

| Block (0, 0)         |                      | Block (1, 0)    |                      |

|----------------------|----------------------|-----------------|----------------------|

| Shared Memory        |                      | Shared Memory   |                      |

| Registers            | Registers            | Registers       | Registers            |

| <b>↓</b> ↓           | <b>↓</b> ↓           | ↓ ↓             | <b>↓ ↓</b>           |

| Thread (0, 0)        | Thread (1, 0)        | Thread (0, 0)   | Thread (1, 0)        |

| + +++ + +++          |                      | A 444 A 444     |                      |

| ↓<br>Local<br>Memory | ◆<br>Local<br>Memory | Local<br>Memory | ↓<br>Local<br>Memory |

| Global<br>Memory     | *                    | *               | •                    |

| Constant<br>Memory   |                      |                 |                      |

| Texture<br>Memory    |                      |                 |                      |

SPIE Medical Imaging 2012

MIC-GPU

11

Grid