#### Engineering High-performance Parallel Algorithms with Applications to Bioinformatics

A Dissertation presented

by

#### Jesmin Jahan Tithi

$\operatorname{to}$

The Graduate School

in Partial Fulfillment of the

Requirements

for the Degree of

#### **Doctor of Philosophy**

$_{\mathrm{in}}$

**Computer Science**

Stony Brook University

December 2015

Copyright by Jesmin Jahan Tithi 2015 ALL RIGHTS RESERVED.

#### Stony Brook University

The Graduate School

Jesmin Jahan Tithi

We, the dissertation committee for the above candidate for the

Doctor of Philosophy degree, hereby recommend

acceptance of this dissertation

Rezaul Chowdhury Assistant Professor, Department Computer Science

Steven Skiena Professor, Department Computer Science

I.V. Ramakrishnan Professor, Department Computer Science

Michael Bender Professor, Department Computer Science

Robert J. Harrison Professor and Director, Institute for Advanced Computational Science - Stony Brook

This dissertation is accepted by the Graduate School

Charles Taber Dean of the Graduate School

#### Abstract of the Dissertation

#### Engineering High-performance Parallel Algorithms with Applications to Bioinformatics

by

Jesmin Jahan Tithi

#### Doctor of Philosophy

in

#### **Computer Science**

Stony Brook University

#### 2015

Since the beginning of the last decade, plateauing of the clock speed of computer processors has forced us to invest more in parallelism — for both hardware and software. This resulted in improvements in computing technologies that have favored parallelism over increased clock speed. Taking advantage of these improvements requires designing algorithms that can leverage parallelism well. In this dissertation, we show how to take advantage of several algorithm design techniques to harness modern heterogeneous parallel architectures for solving problems in bioinformatics efficiently. Our main goal while designing algorithms is to achieve high-performance in terms of running time and scalability. Other desirable goals include energy efficiency, portability and adaptivity.

We solve bioinformatics problems on grids (dynamic programming problems), on graphs (breadthfirst search), and problems that can be solved using spatial trees (Molecular Dynamics using octrees). We present many novel algorithms, algorithm engineering techniques, theoretical analyses and performance evaluations on a range of state-of-the-art parallel architectures including multicores, manycores, and special purpose accelerators. Although we mainly target problems in bioinformatics, the algorithmic techniques we use to solve those problems have general applicability.

For many dynamic programming problems, we show that if we use a *cache-oblivious recursive divide-and-conquer* technique to solve them, the resulting algorithms become highly optimizable, cache-optimal and often have asymptotically better parallelism than their standard iterative counterparts. These algorithms not only have good theoretical bounds, but also perform better than standard iterative and tiled-loop algorithms in terms of running time, scalability, energy-efficiency, cache-adaptivity and portability. Furthermore, it is often possible to improve parallelism of these recursive algorithms without sacrificing cache-optimality by removing *artificial dependencies* among the tasks introduced by the recursive structure of the algorithm.

Breadth-first search is a popular graph traversal algorithm that has many applications in bioinformatics. We show how to use *lock- and atomic instruction-free optimistic parallelization* to improve parallelism and load balancing in a shared-memory parallel breadth-first search (BFS) algorithm. We present several work-efficient parallel BFS algorithms (including one that uses recursive divide and conquer) along with their theoretical and empirical performance analyses on state-of-the-art multicore and manycore architectures.

Spatial trees (e.g., quad tree, octree, k-D tree) are recursive space partitioning data structures that are often used to store biological molecules efficiently. We present octree-based distributed and distributed-shared-memory hybrid near-far approximation algorithms to compute molecular polarization energy. These algorithms outperform all other state-of-the-art Molecular Dynamics packages by orders of magnitude on multicores and clusters of multicores.

We conclude by discussing implications of our work for future parallel algorithm design, and ways to extend our research to other domains.

#### **Dedication Page**

The thesis is dedicated to my parents Md. Jahan Ali and Monju Ara for their endless love, support and encouragement.

## Contents

| С  | Contents        |                                                                |   |  |  |

|----|-----------------|----------------------------------------------------------------|---|--|--|

| Li | List of Figures |                                                                |   |  |  |

| Li | List of Tables  |                                                                |   |  |  |

| 1  | Inti            | roduction                                                      | 1 |  |  |

|    | 1.1             | Part I. Algorithms on grids: Dynamic programming               | 5 |  |  |

|    | 1.2             | Part II. Algorithms on graphs: Breadth-first search            | 7 |  |  |

|    | 1.3             | Part III. Algorithms using spatial trees: Molecular energetics | 8 |  |  |

| Ι  | Al              | gorithms on Grids                                              | 9 |  |  |

| 2  | Exp             | bloiting Spatial Architectures for Edit Distance Algorithms    | 0 |  |  |

|    | 2.1             | Abstract                                                       | 0 |  |  |

|    | 2.2             | Introduction                                                   | 0 |  |  |

|    | 2.3             | Background                                                     | 2 |  |  |

|    |                 | 2.3.1 Spatial Architectures                                    | 2 |  |  |

|    |                 | 2.3.2 Edit Distance                                            | 4 |  |  |

|    |                 | 2.3.2.1 Overview of the Edit Distance Problem                  | 4 |  |  |

|    |                 | 2.3.2.2 Exploitation of Pipeline Parallelism                   | 5 |  |  |

|    | 2.4             | Edit Distance on Spatial Architectures                         | 5 |  |  |

|    |                 | 2.4.1 Designing a Worker                                       | 6 |  |  |

|    |                 | 2.4.1.1 Optimization                                           | 6 |  |  |

|    |                 | 2.4.1.2 Mapping                                                | 8 |  |  |

|    |                 | 2.4.2 Naïve Implementation                                     | 8 |  |  |

|    |                 | 2.4.3 Optimization: Use of Linear Memory Space                 | 8 |  |  |

|    |                 | 2.4.4 Strip Mining                                             | 9 |  |  |

|    |                 | 2.4.4.1 Strip Mining using Memory                              | 9 |  |  |

|    |                 | 2.4.4.2 Strip Mining using PEs' scratchpad memory 2            | 0 |  |  |

|    |                 | 2.4.5 Tiling 2                                                 | 1 |  |  |

|    |                 | 2.4.6 Linear Memory Space Traceback Path                       | 2 |  |  |

|    | 2.5             | Experimental Setup                                             | 3 |  |  |

|    |                 | 2.5.1 Spatial Architecture Performance                         | 3 |  |  |

|    |                 | 2.5.2 Spatial Edit Distance Implementation                     | 4 |  |  |

|    |                 | 2.5.3 x86 Comparison                                           | 4 |  |  |

|    | 2.6             |                                                                | 5 |  |  |

|    |                 |                                                                | 5 |  |  |

|    |                 |                                                                | 7 |  |  |

|    |                 | *                                                              | 7 |  |  |

|    | 2.7             |                                                                | 8 |  |  |

2.8 Conclusion and Future Research

29

| 3 |             | ursive Dynamic Programming With Matrix-multiplication-like Flexible                           |

|---|-------------|-----------------------------------------------------------------------------------------------|

|   |             | nels 30                                                                                       |

|   | 3.1         | Abstract                                                                                      |

|   | 3.2         | Introduction                                                                                  |

|   | 3.3         | Algorithms                                                                                    |

|   |             | 3.3.1 Parenthesis Problem                                                                     |

|   |             | 3.3.2 Protein Accordion Folding                                                               |

|   |             | 3.3.3 Sequence Alignment with General Gap Penalty                                             |

|   |             | 3.3.4 All Pairs Shortest Path Problem                                                         |

|   | 3.4         | Optimizations                                                                                 |

|   | 0.1         | 3.4.1 Hybrid CORDAC                                                                           |

|   |             | 3.4.2 Optimizing Kernel Functions                                                             |

|   |             | 3.4.3     Data Layout     42                                                                  |

|   |             | 3.4.5       Data Layout       42         3.4.4       Auto vs. Explicit Vectorization       43 |

|   |             | 1                                                                                             |

|   | 9 F         |                                                                                               |

|   | 3.5         | Experimental Results                                                                          |

|   |             | 3.5.1 Performance on Shared-Memory Machines                                                   |

|   |             | 3.5.2 Extension to Distributed-Memory Settings                                                |

|   |             | 3.5.3 Shared-Distributed-Shared-Memory Results                                                |

|   |             | 3.5.4 Communication Complexity                                                                |

|   | 3.6         | Conclusions                                                                                   |

|   | C           |                                                                                               |

| 4 |             | he-adaptivity, Bandwidth Benefit and Robustness of Recursive Divide and aquer 54              |

|   | 4.1         | iquer         54           Abstract         54                                                |

|   |             |                                                                                               |

|   | 4.2         | Introduction                                                                                  |

|   | 4.3         | Adaptivity and Robustness                                                                     |

|   | 4.4         | Experimental Results                                                                          |

|   |             | 4.4.1 Robustness                                                                              |

|   |             | Parenthesis Problem                                                                           |

|   |             | Floyd-Warshall's APSP                                                                         |

|   |             | Gap Problem                                                                                   |

|   |             | 4.4.2 Cache-adaptivity                                                                        |

|   | 4.5         | Conclusion                                                                                    |

| _ | ъ           |                                                                                               |

| 5 | Pro<br>rith | vably Efficient Scheduling of Cache-Oblivious Recursive Wavefront Algo-<br>ms 64              |

|   | 5.1         |                                                                                               |

|   |             |                                                                                               |

|   | 5.2         | Introduction                                                                                  |

|   | 5.3         | Deriving recursive wavefront algorithms                                                       |

|   |             | 5.3.1 Constructing completion-time function                                                   |

|   |             | 5.3.2 Deriving a recursive wavefront algorithm                                                |

|   | 5.4         | Applications    75                                                                            |

|   | 5.5         | Scheduling recursive wavefront algorithms                                                     |

|   | 5.6         | Experimental results                                                                          |

|   | 5.7         | Future Research    82                                                                         |

| 0 |             | Designed Clarks a blindering With 11 Al 191                                                   |

| 6 |             | Efficient Cache-oblivious Viterbi Algorithm 83                                                |

|   | 6.1         | Abstract                                                                                      |

|   | 6.2         | Introduction                                                                                  |

|   | 6.3         | Viterbi algorithm using rank convergence                                                      |

|   |             | 6.3.1 Maleki et. al.'s algorithm using rank-convergence                                       |

|   |             | 6.3.2 An improved processor-oblivious algorithm                                               |

| 6.4 | Cache-efficient multi-instance Viterbi algorithm                        | 88 |

|-----|-------------------------------------------------------------------------|----|

| 6.5 | Cache-efficient Viterbi algorithm                                       | 90 |

| 6.6 | Experimental results                                                    | 91 |

|     | 6.6.1 Multi-instance Viterbi: Iterative vs. Recursive                   | 92 |

|     | 6.6.2 Single-instance Viterbi: Efficient recursive vs. Maleki et. al.'s | 93 |

| 6.7 | Conclusions and Future Research                                         | 93 |

### II Algorithms on Graphs

95

| 7 |            | imistic Parallelization: Avoiding Locks and atomic instructions in Shared |                 |

|---|------------|---------------------------------------------------------------------------|-----------------|

|   | 7.1        | nory Parallel BFS Abstract                                                | <b>96</b><br>96 |

|   | 7.1<br>7.2 | Introduction                                                              |                 |

|   | 7.2<br>7.3 | Prior Work                                                                |                 |

|   | 7.3<br>7.4 | Our Contributions                                                         |                 |

|   | 7.4<br>7.5 | Our Parallel BFS Algorithms for Multicores                                |                 |

|   | 1.0        | 7.5.1 Based on Centralized Queues                                         |                 |

|   |            | 7.5.2 Based on Distributed Randomized Work-stealing                       |                 |

|   | 7.6        | Extension to NUMA                                                         |                 |

|   | 7.7        | Discussion: Further Improvements                                          |                 |

|   | 7.8        | Correctness                                                               |                 |

|   | 7.9        | Complexity Analyses                                                       |                 |

|   | 1.5        | 7.9.1 $BFS_C$ (Centralize + Lock)                                         |                 |

|   |            | 7.9.1 $BFS_C$ (Centralize + Bock)                                         |                 |

|   |            | 7.9.3 $BFS_{WS}$ (Work stealing + Lock)                                   |                 |

|   | 7 10       | Experimental Results                                                      |                 |

|   | 0          | 7.10.1 Simulation Environment and Input Graphs                            |                 |

|   |            | 7.10.2 Performance Analysis                                               |                 |

|   |            | 7.10.3 Why Lockfree Does Better Load-balancing than Lock-based            |                 |

|   |            | 7.10.4 Explicit vs. Implicit Work-stealing                                |                 |

|   |            | 7.10.5 Performance of Work-stealing on Intel Xeon Phi                     |                 |

|   | 7 11       | Conclusion and Future Research                                            |                 |

|   |            |                                                                           |                 |

| 8 |            | coretically Optimal Level-synchronous Parallel Work-aware BFS             | 118             |

|   | 8.1        | Abstract                                                                  |                 |

|   | 8.2        | Introduction                                                              |                 |

|   | 8.3        | Algorithm                                                                 |                 |

|   | <b>.</b>   | Theoretically optimal BFS                                                 |                 |

|   | 8.4        | Analysis                                                                  |                 |

|   | 8.5        | Experimental Results                                                      |                 |

|   | 8.6        | Conclusion and Future Research                                            |                 |

|   | 8.7        | Acknowledgment                                                            | 126             |

| п | IA         | Algorithms using Spatial Trees                                            | 127             |

| 9 | Hyb        | orid Algorithm using Octrees: Polarization Energy on Clusters of Mult     | i-              |

|      | id Algorithm using Octrees: Polarization Energy on Clusters of Multi- |     |

|------|-----------------------------------------------------------------------|-----|

| core |                                                                       | 128 |

| 9.1  | Abstract                                                              | 128 |

| 9.2  | Introduction                                                          | 128 |

| 9.3  | Background                                                            | 130 |

| 9.4  | Related Work                                                          | 133 |

|      | Popular Parallel $E_{\rm pol}$ Implementations                        | 133 |

| 9.5    | Our C  | ontributions                                             | 133 |

|--------|--------|----------------------------------------------------------|-----|

|        | 9.5.1  | Load Balancing                                           | 134 |

|        | 9.5.2  | Algorithm                                                | 136 |

|        | 9.5.3  | Analysis of Time Complexity                              | 138 |

| 9.6    | Simula | ation Results                                            | 139 |

|        | 9.6.1  | Dealing with NUMA Effect                                 | 139 |

|        | 9.6.2  | Scalability                                              | 140 |

|        | 9.6.3  | Running Time and Speedup                                 | 140 |

|        | 9.6.4  | Energy Value                                             | 142 |

|        | 9.6.5  | Change in Error and Runtime with Approximation Parameter | 142 |

|        | 9.6.6  | Scalability with Larger Molecule                         | 143 |

|        | 9.6.7  | Comparison with Amber GPU Implementations                | 143 |

|        | 9.6.8  | Full Vs. Half Energy                                     | 144 |

| 9.7    | Conclu | ision                                                    | 145 |

| 9.8    | Ackno  | wledgment                                                | 145 |

| 10 Fut | ure Re | search                                                   | 146 |

# List of Figures

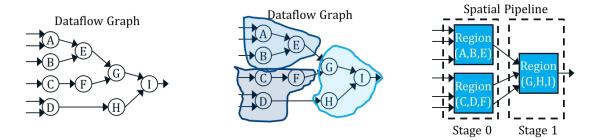

| 2.1          | Spatial programming example. Converting a dataflow graph to a spatial pipeline of regions.                                                                                                                                                | 12 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

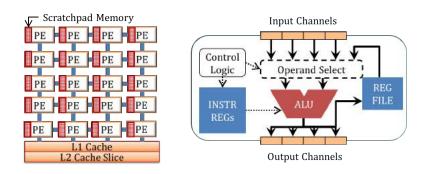

| 2.2          | Example spatial architecture. Network of PEs, scratchpad memory, and caches are shown alongside a PE diagram.                                                                                                                             | 13 |

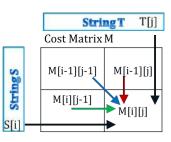

| 2.3          | Solving for edit distance using dynamic programming. The dark-shaded cells are the edits for solving the base cases, and the light-shaded cells are the required minimum edits.                                                           | 14 |

| 2.4          | Data flow dependencies for calculating a cell in edit distance. Dependencies are found along the row and column of the cost matrix, which limits the ability to vectorize.                                                                | 15 |

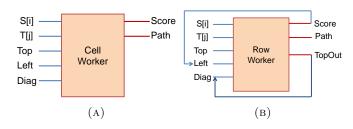

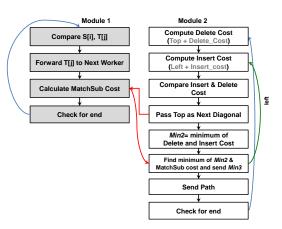

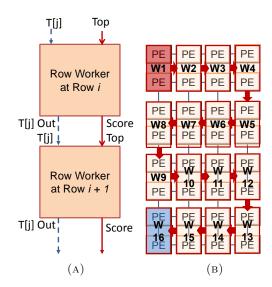

| 2.5          | (A) A simple cell worker that computes a single cell of the cost matrix, (B) An optimized row worker.                                                                                                                                     | 16 |

| $2.6 \\ 2.7$ | Pseudocode for the calculation of a single cell                                                                                                                                                                                           | 16 |

| 2.8          | <ul><li>with other PEs</li></ul>                                                                                                                                                                                                          | 17 |

| 2.9          | of PEs                                                                                                                                                                                                                                    | 18 |

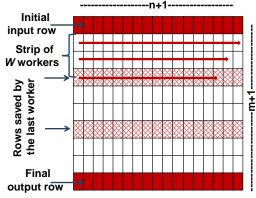

| 2.10         | rows are read from and written to memory, while the intermediate rows use either<br>memory or scratchpad memory                                                                                                                           | 19 |

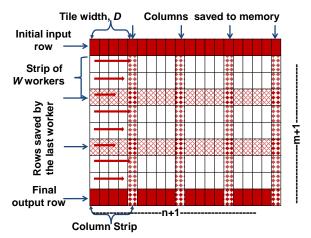

|              | rows are read from and written to memory, while intermediate rows use scratchpad memory. Column results are saved to memory as well.                                                                                                      | 21 |

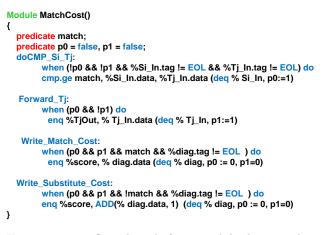

|              | Sample code for a module that matches S[i] with T[j] and computes the cost of cell M[i][j] based on the <i>diagonal</i> cell M[i-1][j-1]                                                                                                  | 24 |

|              | Execution pattern of the x86 based tiled-loop code. The numbers on the tile shows when a tile get executed. Tiles with the same numbers gets executed in parallel.                                                                        | 25 |

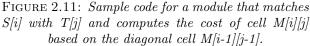

| 2.13         | Results showing that implementations on triggered instruction spatial architecture (TIA) run $50 \times$ faster while consuming $1/100 \times$ energy compared to the optimized single-threaded x86 based tiled-loop implementation.      | 26 |

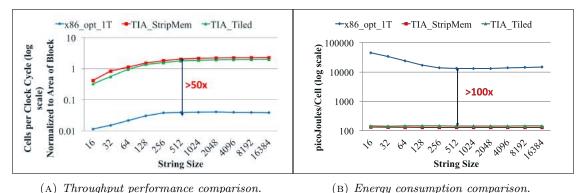

| 2.14         | Comparison of memory, local communication, and scratchpad memory accesses<br>between x86 and TIA based implementations. While register file activity is not<br>shown, TIA local communication numbers include what would be register file |    |

| 3.1          | accesses on x86                                                                                                                                                                                                                           | 27 |

| 0.1          | for matrix multiplication.                                                                                                                                                                                                                | 31 |

| 3.2   | Loop-based parallel codes for the parenthesis problem (PAR-LOOP-PARENTHESIS),<br>Floyd-Warshall's APSP (PAR-LOOP-FW), protein accordion folding (PAR-LOOP-<br>PROTEIN-FOLDING) and the gap problem (PAR-LOOP-GAP). In addition to the<br>parallel <i>for</i> loops already shown, the serial <i>for</i> loops in lines 5 and 7 of LOOP- |     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | GAP and in line 4 of LOOP-PARENTHESIS and PAR-LOOP-PROTEIN-FOLDING can                                                                                                                                                                                                                                                                  | 0.4 |

|       |                                                                                                                                                                                                                                                                                                                                         | 34  |

| 3.3   | A protein accordion fold where each star represents a hydrophobic amino acid                                                                                                                                                                                                                                                            |     |

|       | and each circle a hydrophilic one. The accordion score of this folded sequence is 4 which is not the maximum possible accordion score for this sequence.                                                                                                                                                                                | 37  |

| 3.4   | SOF $(i, j, k)$ counts the number of aligned hydrophobic amino acids when the                                                                                                                                                                                                                                                           | 51  |

| 0.4   | protein segment $\mathcal{P}[i:k]$ is folded only once at indices $(j, j+1)$ . In this figure,                                                                                                                                                                                                                                          |     |

|       |                                                                                                                                                                                                                                                                                                                                         | 37  |

| 3.5   | Parallel cache-oblivious recursive divide-and-conquer (CORDAC) algorithms for                                                                                                                                                                                                                                                           |     |

|       | solving the parenthesis and the protein accordion folding problems. For simplicity,                                                                                                                                                                                                                                                     |     |

|       | we assume $n$ to be a power of 2. Initial function calls are as follows. (1) parenthesis                                                                                                                                                                                                                                                |     |

|       | problem: $A_{par}(c)$ for an $n \times n$ input matrix $c$ and (2) protein accordion folding                                                                                                                                                                                                                                            |     |

|       | $A_{fold}(X)$ , where $X = \langle S[1:n,1:n], F[1:n,1:n] \rangle$ are $n \times n$ input matrices.                                                                                                                                                                                                                                     | 38  |

| 3.6   | Parallel cache-oblivious recursive divide-and-conquer (CORDAC) algorithms for                                                                                                                                                                                                                                                           |     |

|       | solving the gap problem. For simplicity, we assume $n$ to be a power of 2. $A_{gap}(G[1: n, 1:n])$ is the initial function call, where $G[0: n, 0:n]$ is the $(n+1) \times (n+1)$                                                                                                                                                       |     |

|       |                                                                                                                                                                                                                                                                                                                                         | 39  |

| 3.7   |                                                                                                                                                                                                                                                                                                                                         | 42  |

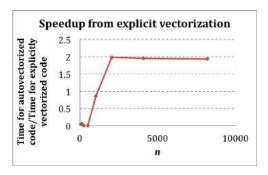

| 3.8   | Benefit of explicit vectorization over autovectorization for FW-APSP code.                                                                                                                                                                                                                                                              | 43  |

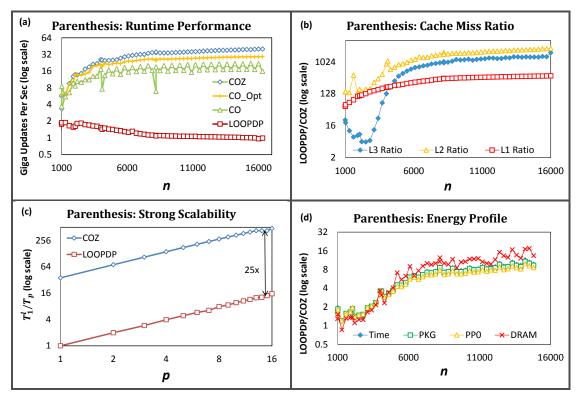

| 3.9   | Parenthesis problem: $(a)$ Giga updates per second achieved by all algorithms, $(b)$                                                                                                                                                                                                                                                    | -   |

|       | ratios of total shared and private cache misses, $(c)$ strong scalability with #cores,                                                                                                                                                                                                                                                  |     |

|       | p when $n$ is fixed at 8192, and $(d)$ ratios of total joule energy consumed by Package                                                                                                                                                                                                                                                 |     |

|       |                                                                                                                                                                                                                                                                                                                                         | 45  |

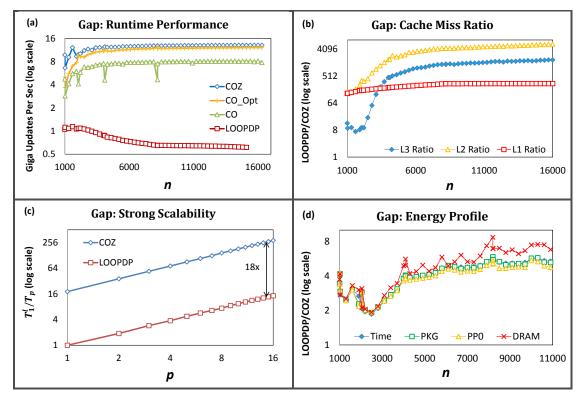

| 3.10  | Gap problem: $(a)$ Giga updates per second achieved by all algorithms, $(b)$ ratios                                                                                                                                                                                                                                                     |     |

|       | of total shared and private cache misses, (c) strong scalability with #cores, $p$                                                                                                                                                                                                                                                       |     |

|       | when $n$ is fixed at 8192, and $(d)$ ratios of total joule energy consumed by Package (PKG), Power Plane 0 (PP0) and DRAM.                                                                                                                                                                                                              | 45  |

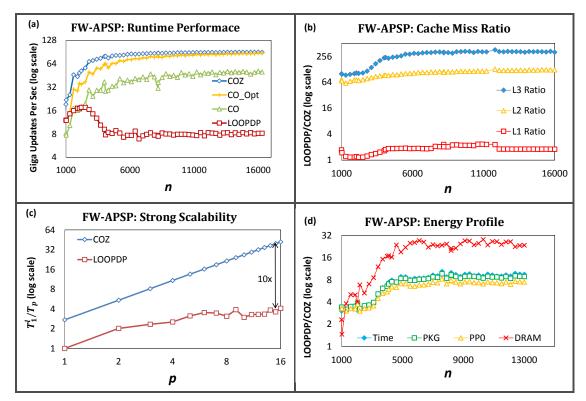

| 3 11  | Floyd-Warshall's all pairs shortest path: (a) Giga updates per second achieved                                                                                                                                                                                                                                                          | 40  |

| 0.11  | by all algorithms, (b) ratios of total shared and private cache misses, (c) strong                                                                                                                                                                                                                                                      |     |

|       | scalability with $\#$ cores, $p$ when $n$ is fixed at 8192, and $(d)$ ratios of total joule                                                                                                                                                                                                                                             |     |

|       |                                                                                                                                                                                                                                                                                                                                         | 46  |

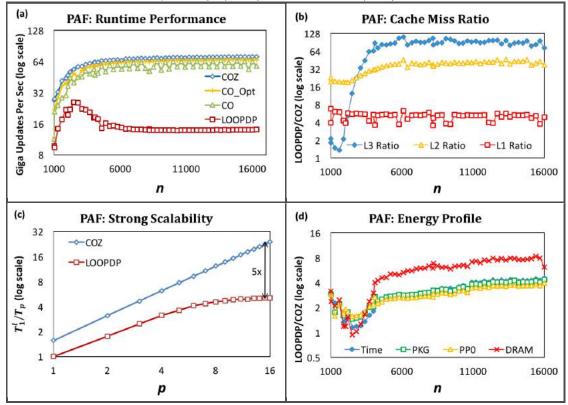

| 3.12  | Protein Accordion Folding: (a) Giga updates per second achieved by all algo-                                                                                                                                                                                                                                                            |     |

|       | rithms, $(b)$ ratios of total shared and private cache misses, $(c)$ strong scalability                                                                                                                                                                                                                                                 |     |

|       | with $\#$ cores, $p$ when $n$ is fixed at 8192, and $(d)$ ratios of total joule energy consumed by Package (PKG), Power Plane 0 (PP0) and DRAM.                                                                                                                                                                                         | 16  |

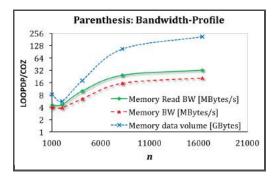

| 2 1 2 | Evidence of better bandwidth utilization of CODRAC, wrt. the iterative algo-                                                                                                                                                                                                                                                            | 46  |

| 0.10  |                                                                                                                                                                                                                                                                                                                                         | 47  |

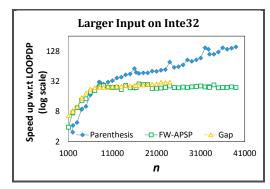

| 3.14  | Speedup w.r.t LOOPDP with larger input sizes on Intel32 machine.                                                                                                                                                                                                                                                                        | 47  |

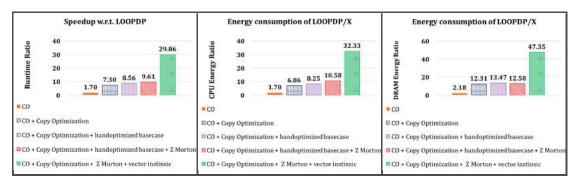

|       | Parenthesis Problem: Itemized breakdown of how much performance gain each                                                                                                                                                                                                                                                               |     |

|       | optimization provides. Here, CO denotes an unoptimized CORDAC algorithm.                                                                                                                                                                                                                                                                | 48  |

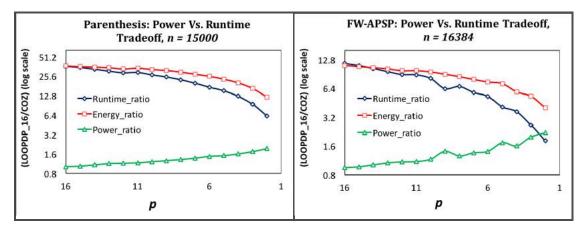

| 3.16  | Power and Runtime Tradeoff. CORDAC has the flexibility to use fewer number of                                                                                                                                                                                                                                                           |     |

|       |                                                                                                                                                                                                                                                                                                                                         | 48  |

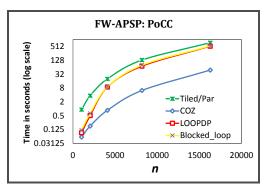

| 3.17  | FW-APSP: Comparison with parallel tiled code generated using polyhedral com-                                                                                                                                                                                                                                                            |     |

|       | piler PoCC [148].                                                                                                                                                                                                                                                                                                                       | 49  |

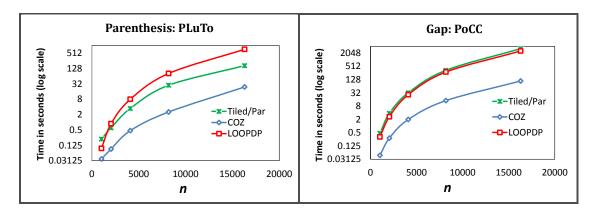

| 3.18  | Parenthesis and Gap Problems: Comparison with parallel tiled code generated                                                                                                                                                                                                                                                             | 50  |

| 2 10  | using polyhedral compilers - PLuTo [29], PoCC [148] and Polly [95] Shared-Distributed-Shared-Memory (SDSM) framework for recursive divide-and-                                                                                                                                                                                          | 50  |

| 9.19  | conquer algorithm with dynamic load-balancing on a cluster of multicores                                                                                                                                                                                                                                                                | 51  |

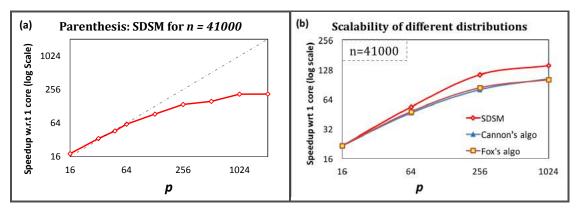

| 3.20  | Parenthesis Problem: (a) Scalability of shared-distributed-shared-memory algo-                                                                                                                                                                                                                                                          | 01  |

| 2.20  | rithm (offloading functions C and B). (b) Performance comparison of different                                                                                                                                                                                                                                                           |     |

|       | work distribution techniques (offloading C only).                                                                                                                                                                                                                                                                                       | 51  |

|       |                                                                                                                                                                                                                                                                                                                                         |     |

| 4.1 | Code snippet for Tiled, CORDAC and Iterative algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

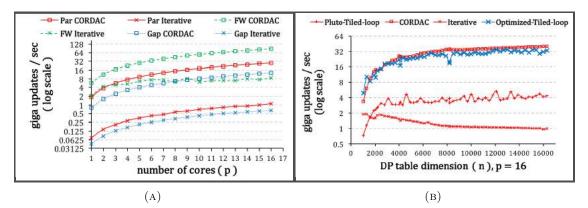

| 4.2 | (A) Rates of updates performed by multithreaded iterative and recursive (COR-<br>DAC) algorithms for the parenthesis problem, Floyd-Warshall's APSP [50], and<br>the Gap problem [39] on $2^{13} \times 2^{13}$ integer matrices, as the number of processing<br>cores varies. (B) Rates of updates performed by multithreaded iterative, recursive<br>and tiled-loop code generated by PLuTo [29] for the parenthesis problem as the<br>matrix dimension varies. The Optimized-Tiled-loop is a hand-optimized version<br>of the tiled code auto-generated by PLuTo.                                                                         | 57       |

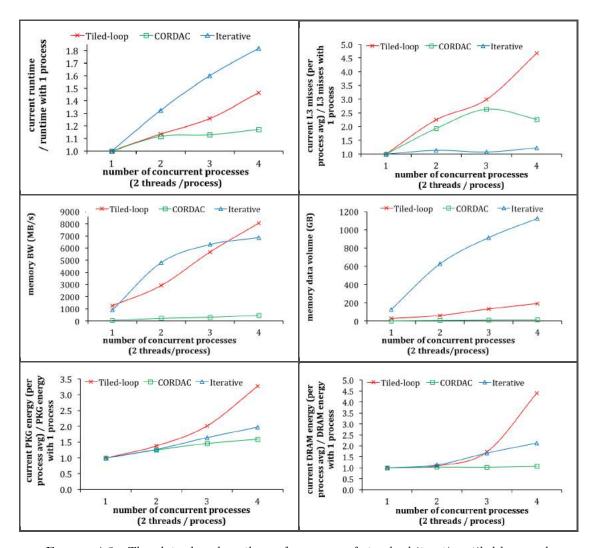

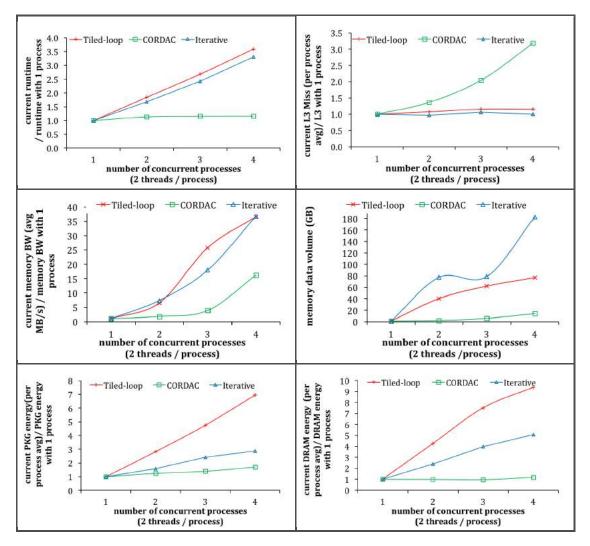

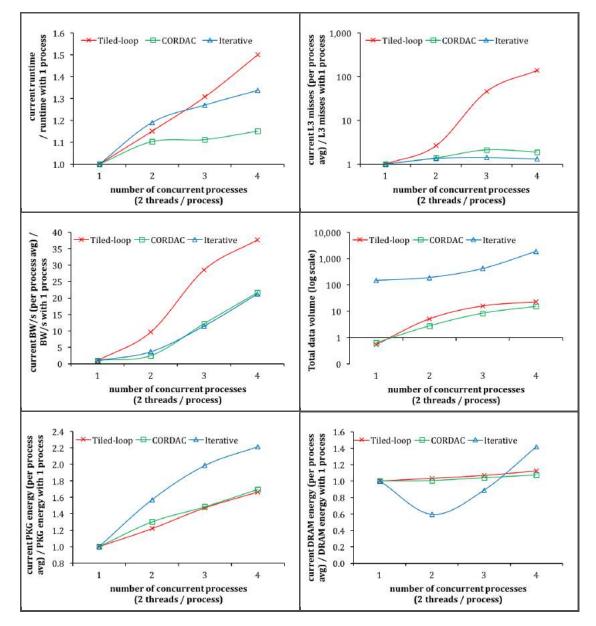

| 4.3 | The plots show how the performances of standard iterative, tiled-loop and recur-<br>sive codes for solving the parenthesis problem (for $n = 2^{13}$ ) are affected when<br>multiple instances of the same program are run on an 8-core Intel Sandy Bridge<br>processor with 20MB shared L3 cache.                                                                                                                                                                                                                                                                                                                                           | 57<br>59 |

| 4.4 | The plots show how the performances of standard-iterative, tiled-loop and recur-<br>sive codes for solving the Floyd-Warshall APSP problem (for $n = 2^{12}$ ) are affected<br>as multiple instances of the same program are run on an 8-core Intel Sandy Bridge<br>processor with 20MB shared L3 cache.                                                                                                                                                                                                                                                                                                                                     | 60       |

| 4.5 | The plots show how the performances of standard iterative, tiled-loop and re-<br>cursive codes for solving the Gap problem (for $n = 2^{13}$ ) are affected as multiple<br>instances of the same program are run on an 8-core Intel Sandy Bridge processor<br>with 20MB shared L3 cache.                                                                                                                                                                                                                                                                                                                                                     | 61       |

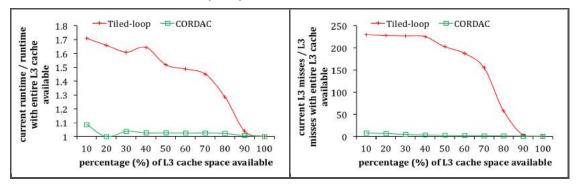

| 4.6 | The plots show how changes in the available shared L3 cache space affect the serial running time and the number of L3 cache misses of tiled-loop and recursive (CORDAC) algorithms for solving the parenthesis problem when $n = 2^{13}$ . The code under test was run on a single core of an 8-core Intel Sandy Bridge processor with 20MB shared L3 cache. A multithreaded Cache Pirate [1, 70] was run on the remaining 7 cores to steal L3 cache space.                                                                                                                                                                                  | 62       |

| 5.1 | Left: The programmer derives the timing functions from a given standard 2-<br>way recursive divide-and-conquer DP algorithm for the parenthesis problem. A<br>matrix region Z has its top-left corner at $(z_r, z_c)$ and is of size $n \times n$ . Right: A<br>recursive divide-and-conquer wavefront algorithm is generated for the parenthesis<br>problem. The programmer derives the algorithm if work-stealing scheduler is used,<br>and the scheduler derives the algorithm if modified hint-accepting space-bounded<br>scheduler (Section 5.5) is used. The algorithm makes use of the timing functions<br>derived by the programmer. | 69       |

| 5.2 | Runtime and cache misses in three levels of caches for 2-way CO (CORDAC),<br>COW and recursive wavefront algorithms for the Parenthesis Problem. All pro-<br>grams were run on 16 core machines in Stampede. All implementations used Cilk<br>Plus's work-stealing scheduler.                                                                                                                                                                                                                                                                                                                                                                | 78       |

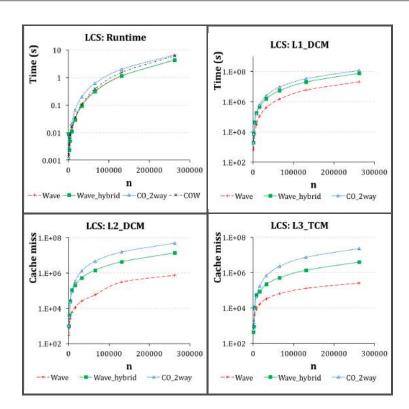

| 5.3 | Runtime and cache misses in three levels of caches for 2-way CO (CORDAC), COW and recursive wavefront algorithms for the LCS Problem. All programs were run on 16 core machines in Stampede. All implementations used Cilk Plus's                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 5.4 | work-stealing scheduler.<br>Runtime and cache misses in three levels of caches for 2-way CO (CORDAC),<br>COW and recursive wavefront algorithms for the 2D FW-APSP Problem. All<br>programs were run on 16 core machines in Stampede. All implementations used                                                                                                                                                                                                                                                                                                                                                                               | 78       |

| 5.5 | Cilk Plus's work-stealing scheduler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 79       |

| 5.6 | Plus's work-stealing scheduler.<br>Runtime and cache misses in three levels of caches for 2-way CO (CORDAC),<br>COW and recursive wavefront algorithms for the LCS Problem. All programs<br>were run on 24 core machines in Comet. All implementations used Cilk Plus's                                                                                                                                                                                                                                                                                                                                                                      | 80       |

|     | work-stealing scheduler.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81       |

| 5.7                                     | Runtime and cache misses in three levels of caches for 2-way CO (CORDAC), COW and recursive wavefront algorithms for the 2D FW-APSP Problem. All programs were run on 24 core machines in Comet. All implementations used Cilk Plus's work-stealing scheduler.                                                                               | 81                                       |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 6.1                                     | Processor-aware parallel Viterbi algorithm using rank convergence as given in Maleki et al. paper [126]. This algorithm is not cache-efficient.                                                                                                                                                                                              | 85                                       |

| 6.2                                     | Processor-oblivious parallel cache-inefficient Viterbi algorithm using rank conver-                                                                                                                                                                                                                                                          |                                          |

| 6.3                                     | gence                                                                                                                                                                                                                                                                                                                                        | 87                                       |

|                                         | rithm                                                                                                                                                                                                                                                                                                                                        | 88                                       |

| 6.4                                     | An efficient cache- and processor-oblivious parallel Viterbi algorithm using rank convergence. VITERBI-MI refers to VITERBI-MI algorithm presented in Section                                                                                                                                                                                | 00                                       |

| 6.5                                     | 6.4                                                                                                                                                                                                                                                                                                                                          | 90                                       |

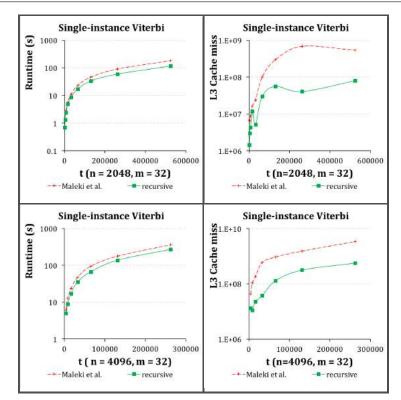

| 6.6                                     | and the multi-instance iterative Viterbi algorithm                                                                                                                                                                                                                                                                                           | 91                                       |

| 0.0                                     | with Maleki et. al.'s algorithm.                                                                                                                                                                                                                                                                                                             | 92                                       |

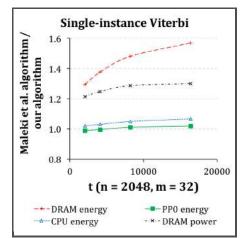

| 6.7                                     | Energy / power consumption of our and Maleki et al.'s algorithms                                                                                                                                                                                                                                                                             | 93                                       |

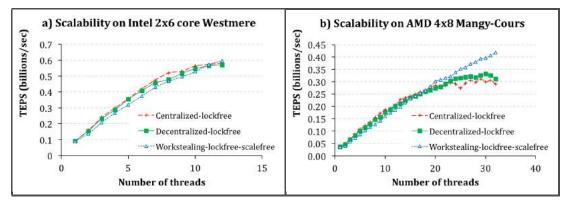

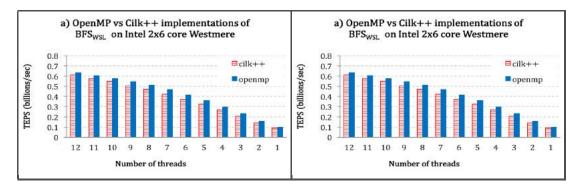

| 7.1                                     | Scalability of lockfree parallel BFS algorithms running on (a) Lonestar and (b) Trestles. All algorithms were run on the Wikipedia graph. All programs were implemented using $Intel^{\textcircled{R}}$ Cilk++ <sup>TM</sup><br>Performance in terms of <i>Traversed Edges Per Second</i> (TEPS) when traversing                             | 111                                      |

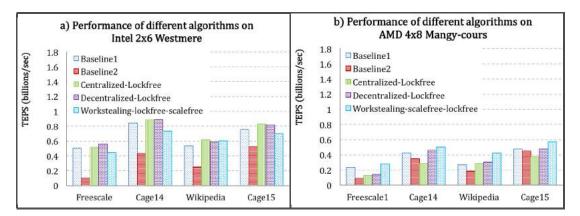

| 7.2                                     | real-word graphs on machines from (a) Lonestar (12 cores) and (b) Trestles (32 cores). All programs were implemented using $Intel^{\mathbb{R}}$ Cilk++ <sup>TM</sup>                                                                                                                                                                         | 112                                      |

| 7.3                                     | Performance in terms of TEPS for Wikipedia Graph on (a) Lonestar (12 cores)                                                                                                                                                                                                                                                                  |                                          |

| 7.4                                     | and (b) Trestles (32 cores). All implementations are in Cilk++<br>Scalability of implicit and explicit work-stealing algorithms (Cilk Plus implemen-                                                                                                                                                                                         | 113                                      |

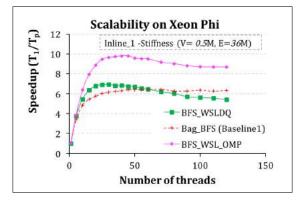

|                                         | tations) on Xeon Phi/MIC.                                                                                                                                                                                                                                                                                                                    | 115                                      |

| 7.5                                     | Scalability of implicit and explicit work-stealing algorithms (Cilk Plus implemen-<br>tations) on Many Integrated Cores: on inline_1 Graph.                                                                                                                                                                                                  | 115                                      |

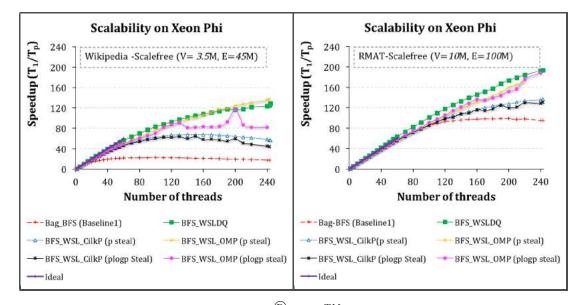

| 7.6                                     | Strong scalability on $Intel^{(R)}$ Xeon <sup>TM</sup> Phi (a) Wikipedia, (b) RMAT-1M-100M.                                                                                                                                                                                                                                                  | 116                                      |

| 8.1                                     | Theoretically optimal work-aware level-synchronous parallel breadth-first search.                                                                                                                                                                                                                                                            | 121                                      |

| 8.2                                     | An efficient way to find starting point in a list of vertices/edges from where a thread should start working on to get even partitioning of work.                                                                                                                                                                                            | 122                                      |

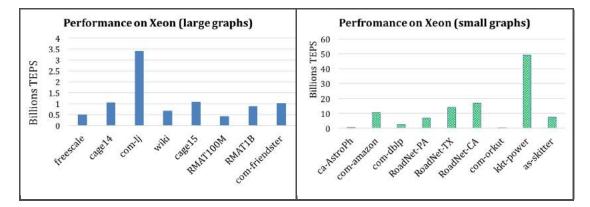

| 8.3                                     | Performance on Xeon (multicores)                                                                                                                                                                                                                                                                                                             | 123                                      |

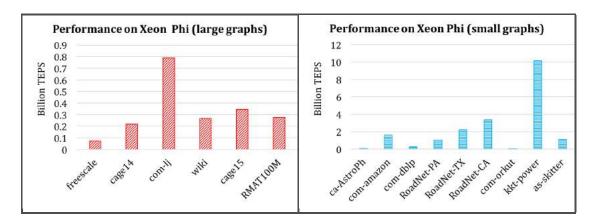

| 8.4                                     | Performance on Xeon Phi (manycores).                                                                                                                                                                                                                                                                                                         | 124                                      |

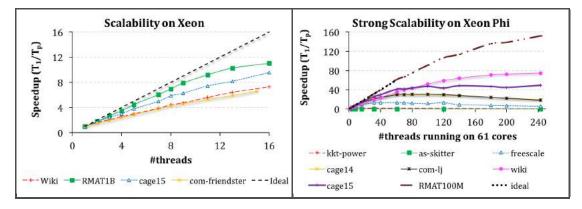

| $\begin{array}{c} 8.5\\ 8.6\end{array}$ | Strong scalability on Xeon and Xeon Phi                                                                                                                                                                                                                                                                                                      | 124                                      |

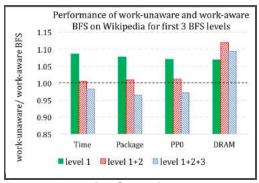

| 0.0                                     | (Package = Socket (CPUs), PP0 = Power Plane0) for the first 3 BFS levels. Here                                                                                                                                                                                                                                                               |                                          |

|                                         | 1 denotes energy consumed at BFS level 1, $1 + 2$ denotes energy consumed at                                                                                                                                                                                                                                                                 |                                          |

| 07                                      | levels 1 and 2, and $1 + 2 + 3$ denotes energy consumed by level 1, 2 and 3                                                                                                                                                                                                                                                                  | 124<br>125                               |

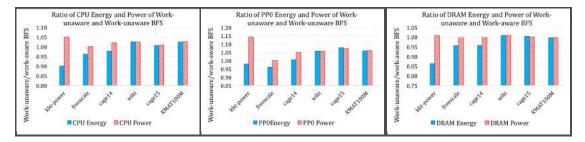

| 8.7                                     | Energy and power efficiency on many real-world graphs                                                                                                                                                                                                                                                                                        | 125                                      |

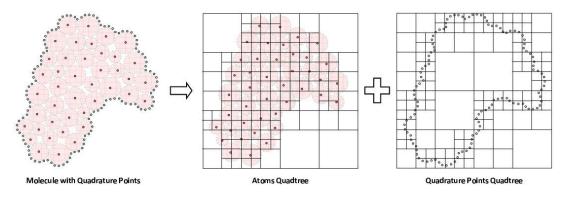

| 9.1                                     | In the Born radius approximation algorithm two octrees are constructed: one for<br>the atoms in the molecule, and the other for the quadrature points. Born radii of<br>all atoms are approximated by recursively traversing both octrees simultaneously.<br>For simplicity, the octrees are drawn as quadtrees. This figure has been reused |                                          |

|                                         | from [45] with permission                                                                                                                                                                                                                                                                                                                    | 132                                      |

| 9.2                                     | Octree-based algorithm for $r^6$ -approximation of Born radii                                                                                                                                                                                                                                                                                | 134                                      |

| 9.3                                     | Octree-based algorithm for approximating $E_{pol}$ from Born radii                                                                                                                                                                                                                                                                           | 134                                      |

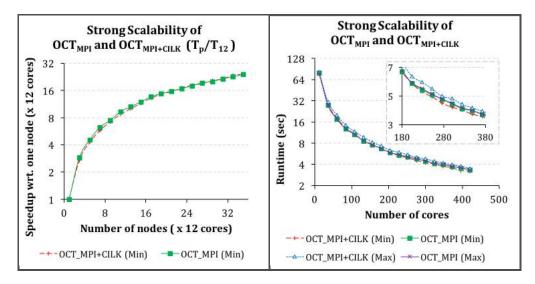

| 9.4                                     | Octree-based distributed- and distributed-shared-memory algorithm Strong scalability with increasing number of cores                                                                                                                                                                                                                         | $\begin{array}{c} 137\\ 140 \end{array}$ |

| 9.5                                     | Shong scalability with increasing number of cores.                                                                                                                                                                                                                                                                                           | 140                                      |

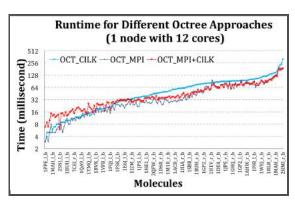

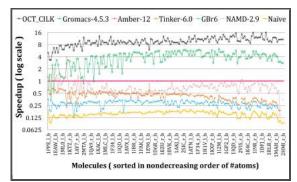

| 9.6  | Performance comparison of different octree based algorithms (results are sorted            |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | by the $OCT_{CILK}$ time)                                                                  | 141 |

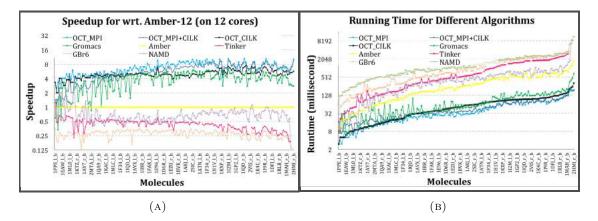

| 9.7  | Performance comparison of different algorithms. Results are sorted by molecule             |     |

|      | size                                                                                       | 141 |

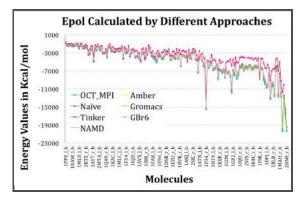

| 9.8  | Energy value computed by different algorithms.                                             | 142 |

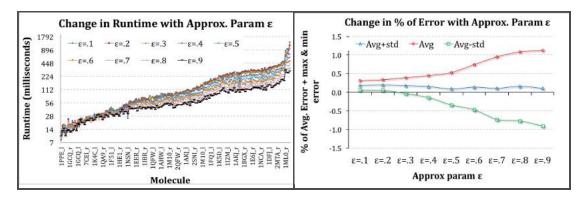

| 9.9  | Change in performance of the $OCT_{MPI+CILK}$ algorithm with approximation pa-             |     |

|      | rameter, $\epsilon$ ; Born Radius $\epsilon$ is fixed at 0.9 and $E_{pol} \epsilon$ varies | 143 |

| 9.11 | Speedup w.r.t. Amber when only half of the energy terms are computed                       | 144 |

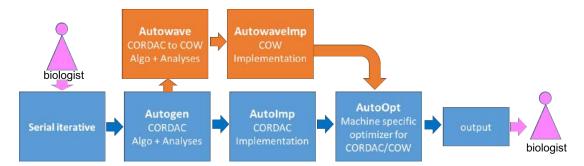

| 10.1 | Ideal pipeline for the automatic generation of efficient recursive algorithms and          |     |

|      | their implementations.                                                                     | 148 |

## List of Tables

| $2.1 \\ 2.2$ | Block architectural parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23              |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.3          | typical modern processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\frac{25}{28}$ |

| 3.1          | Complexities of the iterative and recursive divide-and-conquer (CORDAC) algo-<br>rithms, and the number of invocations of iterative kernels by CORDAC algorithms<br>when run on an input matrix of size $n \times n$ with basecase size $\leq b \times b$ . Flexible<br>kernels are shown on yellow background and asymptotically dominating kernels<br>are shown in bold red. Here, $M =$ size of the cache and $B =$ cache line size.<br>Runtime on $p$ processing elements is $T_p = \mathcal{O}(T_1/p + T_\infty)$ , cache complexity is<br>$Q_p = \mathcal{O}(Q_1 + p(M/B)T_\infty)$ (w.h.p.) when run under Cilk's work-stealing scheduler.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36              |

| 3.2          | System specifications. Intel16E is used for power and energy analyses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43              |